EP2C5 EP2C5T144C8N ALTERA Cyclone II FPGA Развития Борту = OpenEP2C5-C Стандарт |

Сохраните в закладки:

История цены

*История изменения цены! Указанная стоимость возможно, уже изменилось. Проверить текущую цену - >

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Mar-20-2026 | 0.69 руб. | 0.34 руб. | 0 руб. |

| Feb-20-2026 | 0.27 руб. | 0.95 руб. | 0 руб. |

| Jan-20-2026 | 0.9 руб. | 0.66 руб. | 0 руб. |

| Dec-20-2025 | 0.15 руб. | 0.86 руб. | 0 руб. |

| Nov-20-2025 | 0.35 руб. | 0.88 руб. | 0 руб. |

| Oct-20-2025 | 0.3 руб. | 0.58 руб. | 0 руб. |

| Sep-20-2025 | 0.5 руб. | 0.94 руб. | 0 руб. |

| Aug-20-2025 | 0.83 руб. | 0.57 руб. | 0 руб. |

| Jul-20-2025 | 0.19 руб. | 0.84 руб. | 0 руб. |

Новые товары

Новая оригинальная серия Labubu V3 The Monsters Big Into Energy виниловая кукла с лицом модная

Велосипед электрический для взрослых с задним сиденьем и передней корзиной 1000 Вт

Микросхема ANBERNIC RG353V RG353VS 512GB TF карта предварительного загрузки игр PSP DC SS PS1 NDS

ИНСТРУМЕННАЯ ДОСТАВКА НА 4-канальную DJ-систему Pioneer DJ OPUS-QUAD

Кобура в средневековом стиле для пистолета

Устройство чтения карт TF Huawei HuaWei P40mate20/30/40Pro

Автомобильный переключатель регулировки громкости рулевого колеса для VW Jetta 5 MK5 6

Реле RY610024 24V 8A 5PIN

Характеристики

EP2C5 EP2C5T144C8N ALTERA Cyclone II FPGA Развития Борту = OpenEP2C5-C Стандарт |

Описание товара

привет,

ваш заказ составляет менее $8, мы объединены отправить China Post Обычных Малых Пакетов Plus.

нет отслеживания информации, как правило, прибыл в вашей стране 40-70 дней, мы не принимаем спора,

если вы не ждете, рекомендуется приобрести заказ более чем на $8,

ваш заказ более чем на $8, мы объединены организовать для вашей Зарегистрированной Воздушной Почтой Столба Кита,

иметь отслеживая номер запроса информации, общие прибыл в вашей стране составляет от 25 до 50 дней,

пожалуйста, после получения товара, продукты в 5 звезд оценку, спасибо за ваше понимание,

обзор

обзор openep3c5-с является совет по развитию ПЛИС, который состоит из материнской платы DVK601 и FPGA основной плате CoreEP3C5.

openep3c5-с поддерживает дальнейшее расширение с различными опционными вспомогательными досками для конкретного применения. модульная и открытая конструкция делает его идеальным для начала разработки приложений с серии ALTERA Cyclone III FPGA устройств. openep3c5-с позволяет вам начать свой дизайн с процессором Nios II легко и быстро.

что \ ' ы на материнской плате

FPGA CPLD основной плате разъем: для простого подключения основных плат, которые интегрированы в FPGA CPLD чип на борту 8I/Os_1 интерфейс для подключения аксессуаров платы/модули 8I/Os_2 интерфейс для подключения аксессуаров платы/модули 8I/Os_3 интерфейс для подключения аксессуаров платы/модули 8I/Os_4 интерфейс, для подключения аксессуаров платы/модули 16I/Os_1 интерфейс для подключения аксессуаров платы/модули 16I/Os_2 интерфейс для подключения аксессуаров платы/модули 32I/Os_1 интерфейс для подключения аксессуаров платы/модули 32I/Os_2 интерфейс для подключения аксессуаров платы/модули

FPGA CPLD основной плате разъем: для простого подключения основных плат, которые интегрированы в FPGA CPLD чип на борту 8I/Os_1 интерфейс для подключения аксессуаров платы/модули 8I/Os_2 интерфейс для подключения аксессуаров платы/модули 8I/Os_3 интерфейс для подключения аксессуаров платы/модули 8I/Os_4 интерфейс, для подключения аксессуаров платы/модули 16I/Os_1 интерфейс для подключения аксессуаров платы/модули 16I/Os_2 интерфейс для подключения аксессуаров платы/модули 32I/Os_1 интерфейс для подключения аксессуаров платы/модули 32I/Os_2 интерфейс для подключения аксессуаров платы/модули все I/O интерфейсы выше:

capable of being моделируется как USART, I2C, SPI, PS/2, и т. д. способный управлять устройствами, такими как ФРАМ, FLASH, USB, Ethernet, и т. д. разъемы расширения FPGA FPGA булавки доступны на разъемах расширения для подключения SDRAM аксессуар доска ЖК-интерфейс, для подключения LCD22, LCD12864, LCD1602 ОДИН-ПРОВОДНОЙ интерфейс: легко подключается к ОДНИМ ПРОВОДОМ устройств (TO-92 пакет), таких как датчик температуры (DS18B20), электронный регистрационный номер (DS2401) и т. д. зуммер джойстик: пять позиций потенциометр: для регулировки подсветки lcd22 или LCD12864, LCD1602 регулировки контрастности зуммер перемычку джойстик перемычки ОДНИМ ПРОВОДОМ перемычкидля перемычки 16-18:

короткая перемычка для подключения к I/O используется в примере кода открыть перемычку для подключения к другим пользовательских булавки через перемычекThe DVK601 supports a wide range of different core доски, таким образом, некоторые интерфейсы могут быть Не Связаны и бесполезно при подключении к определенным основной плате.

что \ ' ы на CoreEP3C5 EP3C5E144C8N: ALTERA Cyclone III FPGA устройства, который показывает: рабочая Частота: 50 МГц рабочее Напряжение: 1.15 В ~ 3.465 В пакет: QFP144 I/O: 82 LEs: 5 К ОПЕРАТИВНАЯ ПАМЯТЬ: 414kb фап: 2 отладка/Программирование: поддержка JTAG AMS1117-3.3, 3.3 В регулятор напряжения AMS1117-2.5, 2.5 В регулятор напряжения AMS1117-1.2, 1.2 В регулятор напряжения EPCS16, на борту серийного ФЛЭШ-памяти, для хранения кода индикатор питания светодиодов кнопка сброса nCONFIG кнопку: для повторного конфигурирования FPGA чип, эквивалент питания сброс выключатель питания 50 М активным кварцевый генератор 5 В DC jack JTAG интерфейс: для отладки/программирования FPGA булавки расширитель, VCC, ЗЕМЛЯ и все Ввода/вывода доступны на разъемах расширения для дальнейшего расширения LED перемычки, короткие перемычки для управления Светодиодами

EP3C5E144C8N: ALTERA Cyclone III FPGA устройства, который показывает: рабочая Частота: 50 МГц рабочее Напряжение: 1.15 В ~ 3.465 В пакет: QFP144 I/O: 82 LEs: 5 К ОПЕРАТИВНАЯ ПАМЯТЬ: 414kb фап: 2 отладка/Программирование: поддержка JTAG AMS1117-3.3, 3.3 В регулятор напряжения AMS1117-2.5, 2.5 В регулятор напряжения AMS1117-1.2, 1.2 В регулятор напряжения EPCS16, на борту серийного ФЛЭШ-памяти, для хранения кода индикатор питания светодиодов кнопка сброса nCONFIG кнопку: для повторного конфигурирования FPGA чип, эквивалент питания сброс выключатель питания 50 М активным кварцевый генератор 5 В DC jack JTAG интерфейс: для отладки/программирования FPGA булавки расширитель, VCC, ЗЕМЛЯ и все Ввода/вывода доступны на разъемах расширения для дальнейшего расширения LED перемычки, короткие перемычки для управления Светодиодами фотографии

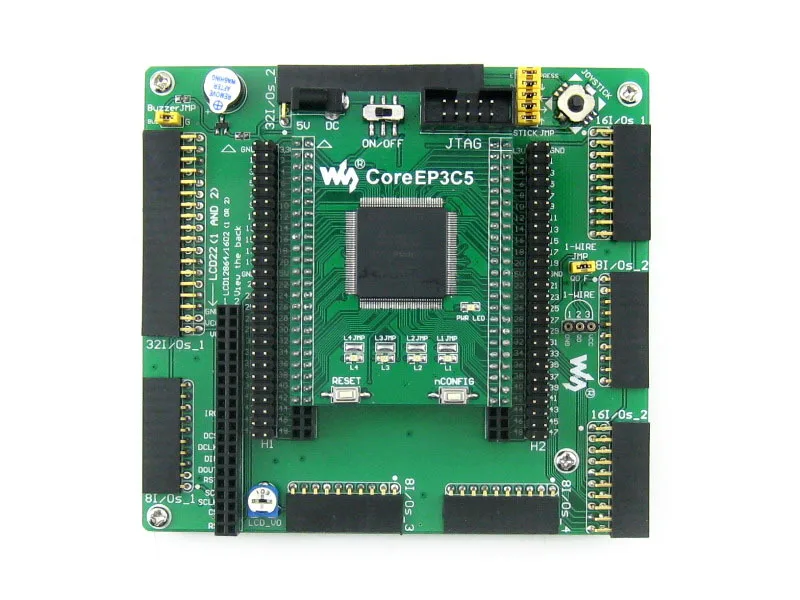

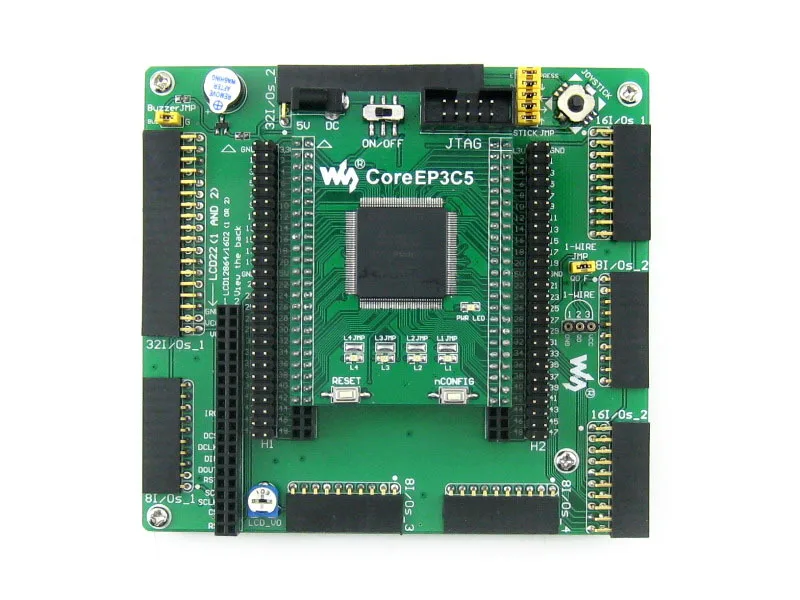

openep3c5-с совет по Развитию

openep3c5-с совет по Развитию

openep3c5-с совет по Развитию Доска вид сзади

материнские Платы DVK601

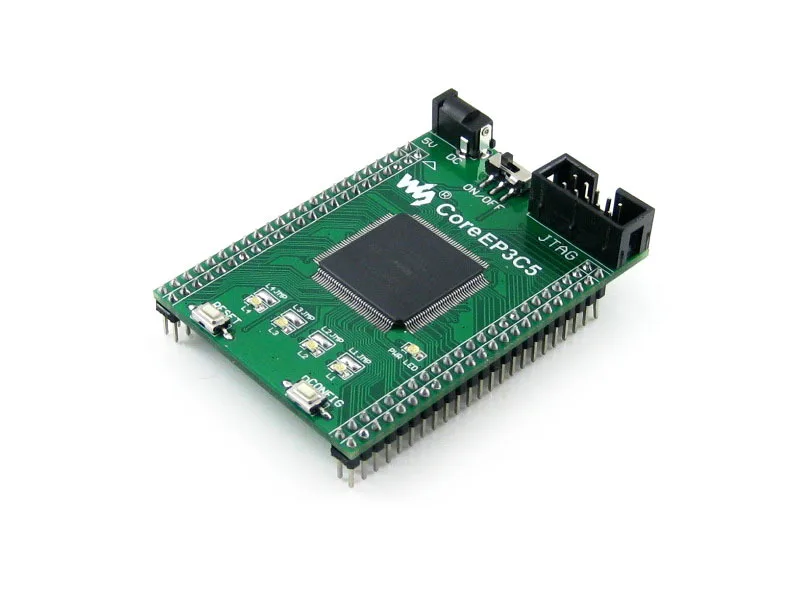

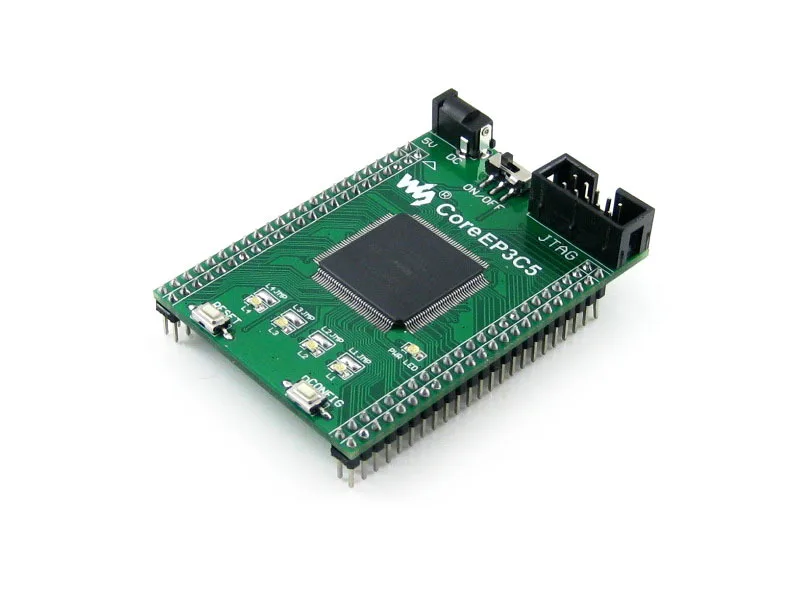

FPGA основной плате CoreEP3C5

FPGA основной плате CoreEP3C5

подключение к различным периферийным устройствам

подключение к 3.2 inch Сенсорный ЖК-

подключение к LCD12864

подключение к LCD1602

подключение к RS232 Совета

подключение к RS485 Доска

подключение к USB UART Совета

подключение к 8 SEG СВЕТОДИОДНЫЕ Табло

подключение к 8 Кнопок

подключение к 5 IO Клавиатуры

подключение к 4x4 Клавиатуры

подключение к EEPROM Совета

нескольких периферийных устройств, подключенных к одному интерфейс

подключение к DataFlash Совета

подключение к Ethernet Доска

подключение к CY7C68013A Плата USB

подключение к NRF24L01 РФ Совет

подключение к Micro SD Для Хранения Совета

подключение к VGA PS2 Совета

подключение к SDRAM Доска

подключение к SDRAM Доска

подключение к любой аксессуар плата вам нужно

примечание: Openep3c5-с не интегрировать любую функцию программирования/отладки, программист/отладчик требуется.

примеры

Openep3c5-с доски развития FPGA поставляется с различными кодами примеры поддерживаемых периферийных устройств, которые дают вам быстрый старт для развития собственного приложения.

периферическойописаниеинтерфейсVerilogVHDLNIOS II CS29GL128PNorFLASH32I/O YAT24CXXEEPROMI2C FM24CXXФРАМI2C AT45DBXXDATAFLASHSPI SD картыFLASHSPI H57V1262GTRSDRAMпараллельно PCF8563RTCI2C DS18B20датчик температуры1-WIRE SP3232последовательной связиUART SP3485последовательной связиUART PL2303USB TO UARTUART FT245USB TO FIFOпараллельно CY7C68013AUSB УСТРОЙСТВАI/O ENC28J60Ethernet контроллерSPI зуммерзвуковое устройство1I/O (ШИМ) PS/2 для клавиатурыустройства вводаPS/2 одной кнопкиустройства ввода---- 4x4 клавиатураустройства ввода8I/Os джойстикустройства ввода5I/Os LEDдисплей устройства---- 8 SEG СВЕТОДИОДНЫЕдисплей устройства13I/Os VGA монитордисплей устройстваVGA символьный ЖК-ДИСПЛЕЙдисплей устройства11I/Os графический ЖК-ДИСПЛЕЙдисплей устройства11I/Os 3.2 дюймов multi-color LCD + сенсорный экрандисплей + устройство Ввода32I/Oотладка/Программирование Интерфейс

Openep3c5-с доски развития FPGA объединяет JTAG интерфейс для программирования/отладки.

JTAG Названия Сигналов и Описание PinНазвание сигналаописание1TCKтактового сигнала2ЗЕМЛЯсигнальная земля3TDOданные устройства4VCC (TRGT)цель питания5TMSJTAG государственного управления машиной6NCнет подключения7NCнет подключения8NCнет подключения9TDIданные устройства10ЗЕМЛЯсигнальная земля Заголовок JTAG Распиновка

Ресурсы для развития

Руководство Пользователя CD включает в себя ресурсы развития перечислены следующим образом:

сопутствующее Программное Обеспечение (Quaters II, NIOS II и т. д.) демо Код (Verilog, VHDL и NIOS II C) схема (PDF) FPGA Документация Развития (Технические и т. д.)пакет Содержит openep3c5-с совет по развитию х 1 4-контактный провод х 2 2-контактный провод х 2 USB кабель х 1 руководство пользователя CD x 1 1

2

2 3

3 4

4 5

5

условия и Условия

1. Payment:

* мы принимаем Сделки в качестве способа оплаты. в настоящее время, вы можете оплатить с помощью Visa, MasterCard и банковский перевод. для получения дополнительной информации об оплате, пожалуйста, перейдите на\ 'Escrow FAQ \ 'чтобы получить более подробную информацию. escrow.aliexpress.com/escrow-faq/payment/what-payment-methods-can-i-use.html

2. Доставка:

* мы отправляем пунктов по Всему Миру!

* пожалуйста, убедитесь, что ваш почтовый адрес 100% правильно.

* все детали будут отправлены в течение 48 рабочих часов после получения оплаты очищается.

* мы \ 'll добавить номер для отслеживания после отправки товара, так что вы можете отслеживать посылку.

3. Политика Возврата:

* мы рады вернуть неиспользованную товар в оригинальной упаковке в течение 14 дней с момента поставки.

* покупатель несет ответственность за раунд (двусторонняя) стоимость доставки.

4. Обратная Связь:

* мы \ 'll оставить ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗИ после получения оплаты очищается.

* если вы \ 're удовлетворены пункта, и наш сервис, пожалуйста, оставьте ПОЛОЖИТЕЛЬНЫЙ ОТЗЫВ, он \ ' ы очень важно для нас.

* после того, как произошло никаких проблем, пожалуйста, свяжитесь с нами в первую очередь. мы \ 'll стараться изо всех сил, чтобы разобраться в ситуации.

пожалуйста, не стесняйтесь обращаться к нам по любым вопросам, на trademanager, или отправить мне сообщение. если вам нужно, чтобы регулировать общую стоимость, пожалуйста, свяжитесь с нами заранее. он \ ' ы наше удовольствие служить вам! мы ценим ваш бизнес!